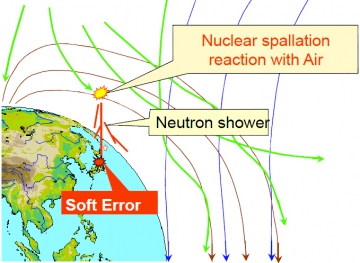

宇宙線によって SRAM に記憶した値が化ける故障が発生する現象はソフトエラーとして広く知られています.半導体の微細化および低電圧化に伴い,ソフトエラーは微細化に伴ってフリップフロップやラッチといったロジック回路部分でも発生しやすくなっているようです.

今回は,そんなロジック回路部分でのソフトエラーの発生しやすさを調べた論文をご紹介.

Impact of Technology and Voltage Scaling on the Soft Error Susceptibility in Nanoscale CMOS [キャッシュ]

http://infocenter.arm.com/help/topic/com.arm.doc.arp0022a/dft08chandra_aitken.pdf

ラッチやフリップフロップは,回路サイズもノードの静電容量も大きいため,ソフトエラーが発生しにくいと考えられていました.この考え方は 90nm 世代までは正しかったのですが,65nm 以降では通用しなくなってきたとのこと.

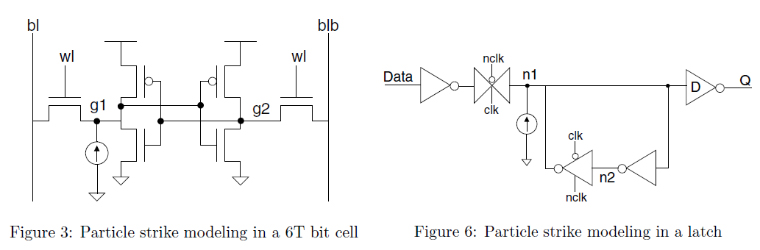

そこで,この論文では 45nm と 65nm の商用のセルライブラリを使ってシミュレーションを行い,SRAM (6T bit cell) とラッチでのソフトエラーの発生しやすさを定量的に検証しています.

検証方法

評価に使用した回路モデルを下図に示します.

ソフトエラーの発生しやすさに影響を与える要因としては次の項目を想定し,これらの条件を変えてシミュレーションを実施しています.

- プロセス

- 動作電圧

- 温度

ソフトエラーは宇宙線によって電荷が発生することによって引き起こされます.そこで,この論文ではビット反転が発生しうる最低の電荷量を Qcrit と定義し,Qcrit の大きさに基づいてソフトエラーの発生しやすさを検証しています.

実際の故障率である FIT 数の評価ではなく,Qcrit の評価にとどめているのは,著者が IP ベンダーである ARM の方だからでしょうか.

結果

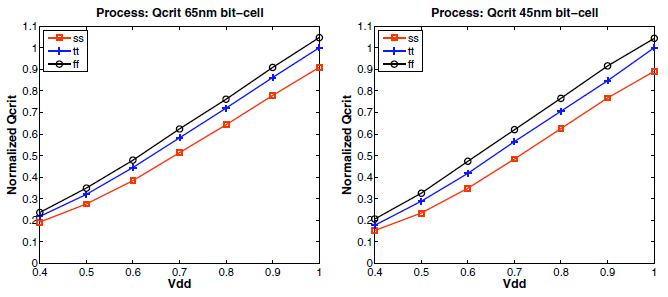

早速ですが,SRAM の結果はこちら.ff,tt,ss は回路の種類を示していて,それぞれ fast,typical,slow の意です.また,Qcrit は 1.0V での typical の値で正規化されています.

45nm も 65nm も電圧が低下するにつれ,Qcrit が小さくなり,ソフトエラーが発生しやすくなっているのがよくわかります.1.0V と 0.4V を比較すると,Qcrit 基準で 5倍程度発生しやすくなっています.また,プロセス依存性では,微細化にともなって Qcrit が小さくなること,およびその傾向は電圧が下がるにつれて大きくなっています.0.4V では,65nm → 45nm で Qcrit が 40% も減少しています.

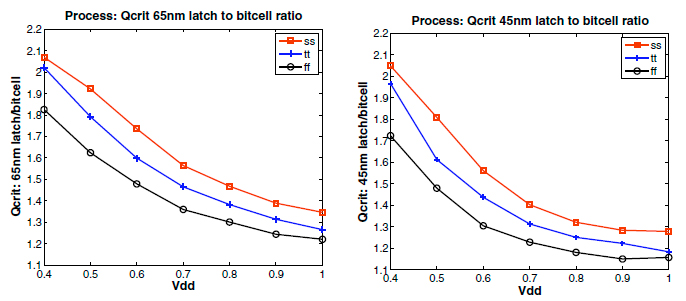

つづいて,ラッチの結果.

SRAM と同じような傾向となっています.ただ,絶対値が異なります.1.0V → 0.4V で SRAM の Qcrit が 80% 減少したのに対し,ラッチは 70% の減少にとどまっています.

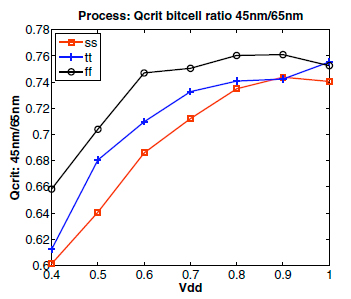

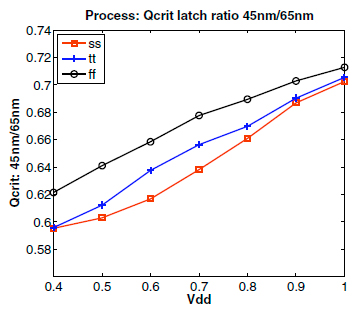

続いて,SRAM とラッチの比較.

電圧が下がるほど,SRAM とラッチの Qcrit の差が大きくなる傾向がでていますが,その比率は最大でもせいぜい 2 程度.また 65nm → 45nm で小さく傾向があり,45nm の 1.0V では 1.19 しかありません.つまり,SRAM と比較したラッチのソフトエラーの発生確率は小さくないことが分かります.

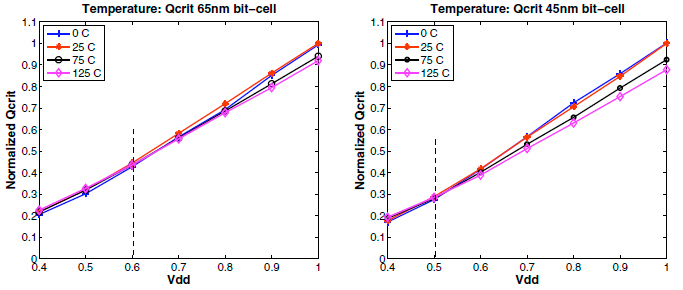

最後に,温度依存性について.

ぱっと見て分かるように,温度依存性はあまり大きくないようです.微細化が進むほど大きくなってはいるものの,65nm で 10%,45nm で 15% しか違いません.

さらに細かく見ていくとおもしろいことが分かります.点線で示された電圧を境に,温度と Qcrit の相関が逆転しています.点線より高い電圧では温度が高いほど Qcrit が小さくなっているのに対し,点線より低い電圧では逆に温度が高いほど Qcrit が大きくなっています.

つまり,電圧が 0.5V とか 0.6V より低い領域では,温度が高いほどソフトエラーが起こりにくくなるようです.直感に反する結論ですが,論文ではこれの要因として「the temperature inversion effect」をあげています.さらっと触れてるだけなので,割と一般的な特性のようですが,私にはよく分かりません.

ソフトエラー対策手法

論文では,ソフトエラー対策についても簡単に紹介されています.対策は大きく 3 つのレベルで行うことが可能です.

- プロセス

- 例えば,ソフトエラーに強い SOI プロセスの採用.

- サーキット

- 例えば,静電容量を増やしたり,記録セルの構成を変えたり,冗長性を持たせたり.

- アーキテクチャ

- 例えば,ECC の採用.

まとめ

65nm → 45nm の微細化によって,Qcrit は 30% 減少する.この傾向は今後微細化が進んでも続くと考えられる.また,1.0V → 0.4V の低電圧化によって Qcrit は 80% 減少する.その上,微細化が進むと,ロジックを構成するラッチやフリップフロップの Qcrit までもが SRAM の 2 倍程度まで小さくなる.

従って,微細化と低電圧化が進むにつれソフトエラーは信頼性の肝となる.これらを解決するには,プロセス,サーキット,アーキテクチャの 3 つのレイヤで対策が必要になる.

感想

微細化が進むにつれ,ロジックもソフトエラーと無縁でなくなってくる,ということを定量的に示している点で興味深い.一方,次の二つの点でやや消化不良の感がある.

- 実際のエラー発生率ではなく Qcrit の値のみで議論している

- シミュレーションで値を算出しているが,実測値との整合性についての議論がない

デバイスの信頼性を議論する場合は,この辺はについて触れた別の文献にも当たる必要がありそう.

コメント